# A COMPACT CHARGE-BASED MOSFET MODEL FOR CIRCUIT SIMULATION

O. C. Gouveia Filho<sup>1</sup>, A. I. A. Cunha<sup>2</sup>, M. C. Schneider<sup>1</sup> and C. Galup-Montoro<sup>1,3</sup>

<sup>1</sup>LINSE - Departamento de Engenharia Elétrica - UFSC - C.P. 476

88 040 900 Florianópolis - SC - Brasil

E-mail: ogouveia@linse.ufsc.br

<sup>2</sup>Departamento de Engenharia Elétrica da Escola Politécnica - UFBA

40210-630 Salvador - BA - Brasil

<sup>3</sup>Texas A & M University - Department of Electrical Engineering

College Station - Texas - 77843-3128 - EUA

#### Abstract

This paper presents a physically based model for the MOS transistor suitable for design and simulation of integrated circuits. The static and dynamic characteristics of the MOSFET are accurately described by single-piece functions of the inversion charge densities at source and drain. A new compact and physical approach to short-channel effects is presented. We have run some tests to compare the performances of our model and widely used MOSFET models.

#### 1.INTRODUCTION

MOSFET models included in circuit simulators can be classified into the following three categories [1]: analytical models, table lookup models and empirical models. Almost all the models in current use are analytical.

Most MOSFET analytical models are based on either the regional approach or surface potential formulations, or semi-empirical equations [2]. Models based on the regional approach use different set of equations to describe the weak and strong inversion regions, generally bridged by using a non-physical curve fitting. Models based on surface potential formulation are inherently continuous; however, they demand the solution of an implicit equation for the surface potential. Semi-empirical models are usually neither scalable nor suited for statistical analysis.

This paper presents a charge-based physical model [2-4] of the MOSFET. All the large and small-signal characteristics are given by single-piece expressions with infinite order of continuity (C∞ functions). Our model preserves the structural source-drain symmetry of the transistor and uses a reduced number of physical

parameters. It is also charge-conserving and has explicit equations for its 16 transcapacitances. Moreover, short-channel effects are easily introduced by using a charge-based model.

The fundamentals of our model are presented in Section 2 while its implementation in a circuit simulator is described in Section 3. Section 4 presents some examples of simulation to compare the relative performances of our model, EKV, SPICE3, and BSIM3v3 models.

# 2. FUNDAMENTALS

The fundamental assumption of our model is the linear dependence of the inversion charge density  $Q_I'$  on the surface potential  $\phi_S$  [2, 6], for a given gate-to-bulk voltage  $(V_G)$ :

$$dQ_{I}' = nC_{ox}'d\phi_{S} \tag{1}$$

where  $C'_{ox}$  is the oxide capacitance per unit area and n is the slope factor, slightly dependent on the gate voltage [2-5].

Equation (1) has allowed the model in [2] to be fully formulated in terms of the inversion charge densities at the source ( $Q'_{1S}$ ) and drain ( $Q'_{1D}$ ) channel ends. The relationship between the inversion charge density and the terminal voltages is [4,7]

$$V_{P} - V_{C} = \phi_{t} \left[ \frac{Q'_{IP} - Q'_{1}}{nC'_{OX} \phi_{t}} + \ln \left( \frac{Q'_{I}}{Q'_{IP}} \right) \right]$$

(2)

where  $V_C$  is the channel voltage,  $V_P$  is the pinch-off voltage,  $Q'_{IP}$  is the inversion charge density at pinch-off and  $\phi_t$  is the thermal voltage. All the voltages are referred to the local substrate, as in [3-5]. Equation (2) cannot be solved analytically for  $Q'_{I}$  but it can be approximated by the following expression [4]:

$$q = \ln \left[ 1 + \frac{e^{u-1}}{1 + k(u) \ln(1 + e^{u-1})} \right]$$

(3)

with

$$k(u) = 1 - \frac{84.4839}{u^2 + 150.8640}$$

(4)

where

$$u = \frac{V_p - V_{S(D)}}{\phi_t}$$

and  $q = -\frac{Q'_{IS(D)}}{nC'_{OX}\phi_t}$  (5)

## 3. MOSFET MODEL

#### 3.1. Short and narrow channel effects

If velocity saturation effects are negligible, the drain current of a MOS transistor can be written as

$$I_{D} = f(V_{P}, V_{S}) - f(V_{P}, V_{D})$$

(6)

For a long and wide transistor the pinch-off voltage is a function of  $V_G$  only, but for short and narrow channel devices  $V_P$  is a function of  $V_G$ ,  $V_S$  and  $V_D$ . To keep the symmetry of equation (6),  $V_P$  is modeled as

$$V_{P}(V_{G}, V_{S}, V_{D}) = V_{P0}(V_{G}) + \frac{\sigma}{n}(V_{D} + V_{S})$$

(7)

$V_{P0}(V_G)$  is the pinch-off voltage at equilibrium  $(V_D\!=\!V_S\!=\!0)$  and is given by

$$V_{P0} = \left( \sqrt{V_{G} - V_{TO} + \phi_{o} + \gamma \sqrt{\phi_{o}} + \left(\frac{\gamma'}{2}\right)^{2}} - \frac{\gamma'}{2} \right)^{2} - \phi_{o}(8a)$$

$$\gamma' = \gamma - \frac{\epsilon_o \epsilon_{Si}}{C'_{OX}} \left[ \frac{2.\eta_L}{L_{eff}} - \frac{3.NP.\eta_W}{W_{eff}} \right] \sqrt{\phi_o}$$

(8b)

where  $\phi_o$  is a fitting parameter whose value is about twice the Fermi potential  $(2\phi_F)$  and  $V_{TO}$  is the threshold voltage at equilibrium.  $\gamma$  is the body effect coefficient of a wide, long-channel device.  $\gamma'$  is the body effect coefficient modified to include short and narrow channel effects.  $\eta_L$  and  $\eta_W$  are parameters to be adjusted;  $L_{eff}$  and  $W_{eff}$  are the effective length and width, respectively. The parameter  $\sigma$  accounts for the drain induced barrier lowering (DIBL) [7] and is proportional to  $1/L^2_{eff}$ .

# 3.2 Mobility reduction [4]

The mobility reduction due to the vertical field is modeled by

$$\mu = \frac{\mu_{o}}{1 + \theta \cdot \gamma \sqrt{V_{PO} + \phi_{o}}} \qquad (9)$$

where  $\mu_{\text{o}}$  is the zero bias mobility, and  $\theta$  is a fitting parameter.

#### 3.3 Velocity saturation

The effect of velocity saturation in our model is based on the expression [6] below:

$$\mu_{S} = \frac{\mu}{1 + \frac{\mu}{v_{lim}} \frac{d\phi_{S}}{dx}}$$

(10)

The substitution of both the approximations (1) and (10) into the differential equation of the drain current leads, after integration along the channel, to [4, 6]

$$I_{D} = \frac{\mu W_{\text{eff}}}{C_{\text{OX}} L_{\text{eq}}} \frac{1}{1 + \frac{\left| Q_{\text{is}} - Q_{\text{iD}}^{\prime} \right|}{O'_{\text{c}}}} \frac{\left[ (Q_{\text{is}}^{\prime 2} - Q_{\text{iD}}^{\prime 2}) - 2nC_{\text{OX}}^{\prime} \phi_{\text{c}} (Q_{\text{is}}^{\prime} - Q_{\text{iD}}^{\prime}) \right]}{2n} (11)$$

$$Q'_{A} = n.C'_{OX}.L_{eq} \frac{v_{lim}}{u}$$

(12)

$v_{lim}$  is the saturation velocity and  $L_{eq} = L_{eff}$  -  $\Delta L$ . The channel length modulation ( $\Delta L$ ) is modeled as in [7]. The maximum current that can flow in the channel occurs when saturation velocity is reached:

$$I_{D} = -Wv_{lim}Q'_{ID} \tag{13}$$

Equating (11) to (13) allows one to calculate the value of Q'<sub>ID</sub> which corresponds to saturation

$$\begin{aligned} &Q'_{IDSAT} = Q'_{IS} - nC'_{OX}\phi_t - \\ &- Q'_{A} \left[ 1 - \sqrt{1 - \frac{2(Q'_{IS} - nC'_{OX}\phi_t)}{Q'_{A}} + \frac{(nC'_{OX}\phi_t)^2}{{Q'_{A}}^2}} \right] (14) \end{aligned}$$

V<sub>DSSAT</sub> is calculated from (2).

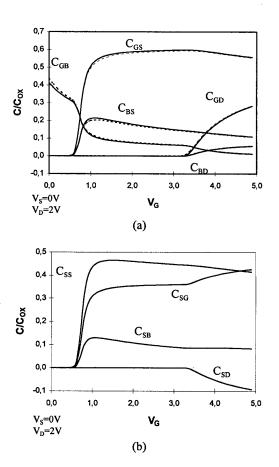

#### 3.4 Charge equations and capacitances

Models that do not conserve charge generate critical errors for the analysis and design of a variety of widely employed MOS circuits such as switched capacitors, switched current and dynamic memories. Charge nonconservation occurs due to the use of capacitance models instead of charge models [8]. Our model is charge-based and has explicit equations for the source, drain, bulk, and gate charges. The charge equations in our model are continuous and have continuous derivatives in all regions of operation, allowing for the calculation of the 16 MOSFET (trans)capacitances [2].

#### 4. RESULTS

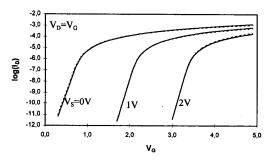

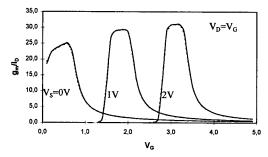

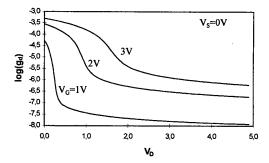

The results shown in figures 1 to 3 correspond to the tests 1 to 3 suggested in [9] to evaluate the performance of a model. They show that our model is continuous

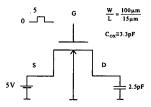

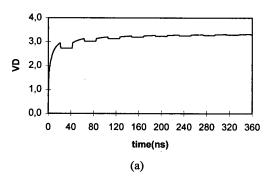

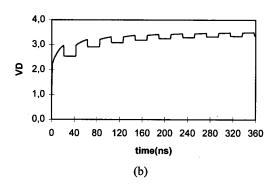

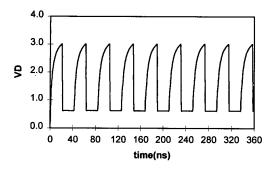

from weak to strong inversion and represents well the moderate inversion region. The plot of the ratio  $g_{mg}/I_D$  versus  $V_G$  presents the expected shape. No discontinuities are observed in  $g_{ds}$ . The DC characteristics of our MOSFET model are in close agreement with those of the EKV model. Figure 4 shows 9 independent MOSFET (trans)capacitances. All the curves are continuous and vary smoothly. A test to verify charge conservation in the sample-hold circuit shown in figure 5 was performed using both our model and SPICE3 from SMASH [10], as well as BSIM3v3 from T-Spice[11]. Figure 6 shows the simulation results. Our model and BSIM3v3 give results consistent with the physical behavior while SPICE3 does not.

## 5. CONCLUSIONS

A compact MOSFET model for circuit simulation has been presented. Simulations using NMOS transistor have shown that the proposed model attains the criterion of continuity. The simulation of a sample-hold circuit showed that our model as well asBSIM3v3 conserve charge, while the SPICE3 model does not. Some advantages of our model over BSIM3v3 are the use of compact expressions to describe all regions of operation as well as a smaller number of device parameters.

Fig.1. log(I<sub>D</sub>) x V<sub>G</sub> for our model \_\_\_\_\_ EKV model -----

Fig. 2. g<sub>m</sub>/I<sub>p</sub> x V<sub>G</sub> for our model \_\_\_\_\_ EKV model -----

Fig. 3. log(g<sub>ds</sub>) x V<sub>D</sub> for our model \_\_\_\_\_ EKV model -----

Fig. 4. (a) Comparisons between the 5 capacitances available in EKV and those of our model (b) 4 capacitances in our model that are not modeled in EKV. The simulations were run in SMASH

Fig. 5. Sample-hold circuit employed to verify charge conservation

(c)

Fig. 6. - Simulation of the sample-hold circuit (a) our model,

(b) BSIM3v3, (c) SPICE3

#### Acknowledgments

The authors would like to thank CAPES and CNPq (from the Brazilian Ministries of Education and Science and Technology) for the financial support, and Dolphin Integration, France for licensing SMASH simulator.

#### References

- N. Arora, "MOSFET Models for VLSI Circuit Simulation - Theory and Practice", Springer-Verlag, Wien, 1993.

- [2] A.I.A. Cunha, M.C. Schneider and C. Galup-Montoro, "An explicit physical model for the long-channel MOS transistor including small-signal parameters", Solid-State *Electronics* Vol.38, n° 11, pp. 1945-1952, 1995.

- [3] A.I.A. Cunha, O. C. Gouveia Filho, M.C. Schneider and C. Galup-Montoro, "A current-based model of the MOS transistor", Proc. 1997 Int. Symposium on Circuits and Systems, pp. 1608-1611, Hong-Kong, June 1997.

- [4] A.I.A. Cunha, "A model of the MOS transistor for integrated circuit design", Ph.D. Thesis (in Portuguese), Universidade Federal de Santa Catarina, Dec. 1996.

- [5] C. C., Enz, F. Krummenacher and E. A. Vittoz, "An analytical MOS transistor model valid in all regions of operation and dedicated to low-voltage and low-current applications", Analog Integrated Circuits and Signal Processing Journal, vol. 8, pp. 83-114, July 1995.

- [6] M. A. Maher and C.A. Mead, "A physical chargecontrolled model for MOS transistors", in P. Losleben (ed), Advanced research in VLSI. Cambridge, MA: MIT Press, 1987.

- [7] K. Lee, M. Shur, T. A. Fjeldly and T. Ytterdal, "Semiconductor device modeling for VLSI", Prentice Hall, Englewoods Cliffs, 1993.

- [8] P. Yang, B.D. Epler, and P.K. Chaterjee, "An investigation of the charge conservation problem for MOSFET circuit simulation", *IEEE Journal of Solid-State Circuits*, vol. sc-18, n°1, pp. 128-138, Feb. 1983.

- [9] Y.P. Tsividis and K. Suyama, "MOSFET modeling for analog circuit CAD: problems and prospects", *IEEE Journal of Solid-State Circuits*, vol. 29, n°3, pp. 210-216, Mar. 1994.

- [10] SMASH users manual, Dolphin Integration, Meylan, France, 1995.

- [11] T-Spice Pro user Manual, Tanner Tools, Pasadena, CA, EUA, 1996.