# A SINGLE-PIECE CHARGE-BASED MODEL FOR THE OUTPUT CONDUCTANCE OF MOS TRANSISTORS

M. C. Schneider<sup>1</sup>, C. Galup-Montoro<sup>1,3</sup>, O. C. Gouveia Filho<sup>1</sup> and A. I. A. Cunha<sup>2</sup>

<sup>1</sup>LINSE - Departamento de Engenharia Elétrica - UFSC - C.P. 476

88 040 900 Florianópolis - SC - Brasil

E-mail: marcio@linse.ufsc.br

<sup>2</sup>Departamento de Engenharia Elétrica da Escola Politécnica - UFBA

40210-630 Salvador - BA - Brasil

<sup>3</sup> Department of Electrical Engineering - Texas A & M University

College Station - Texas - 77843-3128 - USA

#### Abstract

This paper presents a physically based model of the MOSFET output conductance. The drain current and the output conductance of the MOS transistor are accurately described by single-piece functions of the inversion charge densities at source and drain. Carrier velocity saturation, channel length modulation (CLM) and drain induced barrier lowering (DIBL) are included in a single-piece analytical model. The results herein can be readily applied for first order analog circuit hand calculation.

## 1. Introduction

Almost all the MOSFET models included in circuit simulators use the regional approach and some non-physical curve interpolation to bridge the linear and saturation regions [1-4]. A good MOSFET model should exhibit continuity not only in the drain current but also in the output conductance. The effects of carrier velocity saturation, CLM, DIBL and substrate current induced body effect (SCBE) must be taken into account to calculate the output conductance of a MOSFET.

In the classical approach to model the saturation region, the output conductance is assumed to be proportional to the (saturation) drain current and inversely proportional to the Early voltage  $V_A$  [1], a constant parameter in first order models such as SPICE1. However, it is widely known that a constant Early voltage is inadequate to model the output conductance for the simulation of analog circuits. Other models [2,4,11] use smoothing functions to unify the linear and saturation regions. However, they demand the extraction of parameters which neither have a simple physical interpretation nor

are easy to extract. Another drawback of some simulators is that the carrier velocity saturation model is only valid in strong inversion [1, 2, 5, 6], but not in weak inversion, where the channel is almost equipotential [1]. Consequently, saturation is modeled with a physical background in strong inversion while, on the other hand, it is defined in an empirical manner [5, 8] in weak and moderate inversion.

This paper presents a charge-based physical model of the MOSFET output conductance, valid from weak to strong inversion. Our model includes velocity saturation effects, CLM and DIBL. Impact ionization effects can be easily included in our model by adding a substrate current such as in [2]. A physical definition of the MOSFET output conductance in terms of a saturation charge is proposed. From the basic definition of saturation charge, alternative definitions of saturation in terms of current or voltage can be derived. A simple expression for the output conductance showing its dependence on bias is given.

## 2. MOSFET charge-based current model

The basic assumption of our model is the linear dependence of the inversion charge density  $Q'_1$  on the surface potential  $\phi_S$  [7, 9], for a given gate-to-bulk voltage  $(V_G)$ :

$$dQ_{I}' = nC_{ox}'d\phi_{S}$$

(1)

where  $C'_{ox}$  is the oxide capacitance per unit area and n is the slope factor, slightly dependent on the gate voltage.

The effect of velocity saturation in our model is based on the expression [7] below:

$$\mu_{S} = \frac{\mu}{1 + \frac{\mu}{v_{w}} \frac{d\phi_{S}}{dx}}$$

(2)

where the mobility  $\boldsymbol{\mu}$  is a function of the gate -to-bulk potential  $V_G$  only and  $v_{lim}$  is the saturation velocity.

The substitution of both the approximations (1) and (2) into the differential equation of the drain current leads, after integration along the channel, to [7,8]

$$I_{D} = \frac{\mu W_{eq}}{C_{ox}' L_{eq}} \frac{1}{1 + \frac{|Q_{1s}' - Q_{D}'|}{Q_{s}'}} \frac{\left[Q_{1s}'^{2} - Q_{1D}'^{2} - 2nC_{ox}'(Q_{1s}' - Q_{1D}')\right]}{2n}$$

(3)

where

$$Q'_{A} = n.C'_{ox}.L_{eq}.U_{CRIT}$$

and  $U_{CRIT} = \frac{v_{lim}}{\mu}$  (4)

$\phi_t$  is the thermal potential and  $L_{eq}$  is the transistor electrical length.

The charge-based expression (3) to calculate the drain current includes the effects of diffusion, drift and carrier velocity saturation. (3) is a general expression that is valid from weak to very strong inversion. The charge in the denominator models velocity saturation; the term  $|Q'_{is} - Q'_{iD}|$  correctly represents the channel potential in strong as well as in weak inversion.

## 3. Operation in saturation

The maximum current that can flow in the channel occurs when the maximum velocity in the inversion layer reaches the saturation velocity. In this case:

$$I_{D} = -W V_{lim} Q'_{lD} \tag{5}$$

$I_{D} = -Wv_{lim}Q'_{lD} \tag{5}$  Equating (3) to (5) allows one to calculate  $Q'_{IDSAT}$ , the value of Q'<sub>ID</sub> which corresponds to the onset of

$$Q'_{IDSAT} = Q'_{IS} - nC'_{OX}\phi_t - Q'_A \left[1 - \sqrt{1 - \frac{2(Q'_{IS} - nC'_{OX}\phi_t)}{Q'_A} + \frac{(nC'_{OX}\phi_t)^2}{{Q'_A}^2}}\right]$$

Equation (6) is a general definition, for any inversion level, of the MOSFET inversion charge at the onset of saturation. (6) can be readily interpreted if one assumes  $|Q'_{IS}| \ll Q'_{A}$ . This inequality is valid for all inversion conditions but very strong inversion. In this case, (6) can be approximated by a second order power series:

$$Q'_{IDSAT} = \frac{\phi_t}{U_{CRIT}.L_{eq}} \left( 1 - \frac{Q'_{IS}}{2nC'_{ox}\phi_t} \right) Q'_{IS}$$

(7)

Eqn.(7) shows that the saturation charge is a very small fraction, equal to  $\phi_t/(U_{CRIT}.L_{eq})$  , of the inversion charge at source in weak inversion ( $|Q'_{IS}| \ll nC'_{ox}\phi_t$ ). For moderate and strong inversion, the saturation charge is a larger fraction of Q'<sub>IS</sub> but is still much smaller than Q'<sub>IS</sub> as long as  $|Q'_{IS}| \ll Q'_{A}$ .

Expressing the inversion charge density Q'<sub>IS</sub> at source in terms of the drain current by means of (3) and using the approximation  $|Q'_{is}| \ll Q'_A$ , (7) can be rewritten as

$$\frac{\dot{Q_{IDSAT}}}{\dot{Q_{IS}}} \cong \frac{\phi_t}{U_{CRIT} \cdot L_{eq}} \frac{\sqrt{1 + i_d} + 1}{2}$$

(8)

where  $i_d = I_D/I_S$  is the normalized saturation current and

$$I_{\rm S} = \mu n C_{\rm ox}' \frac{W}{L} \frac{\phi_{\rm t}^2}{2} \tag{9}$$

is the normalization current [10].

Recalling the charge-voltage relationship from [4,10]:

$$\frac{V_{P} - V_{S(D)}}{\phi_{t}} = \frac{Q_{IP}^{'} - Q_{IS(D)}^{'}}{nC_{ox}\phi_{t}} + ln \left(\frac{Q_{IS(D)}^{'}}{Q_{IP}^{'}}\right)$$

(10)

V<sub>DSSAT</sub>, the drain-to-source voltage for which the maximum velocity of the carriers is equal to the saturation velocity, can be calculated as

$$V_{DSSAT} \cong \phi_t \left[ ln \left( \frac{U_{CRIT}, L_{eq}}{\phi_t} \right) + \sqrt{1 + i_d} - 1 \right]$$

(11)

In (10)  $V_P$  and  $Q_{IP}$  are the pinch-off voltage and the inversion charge density at pinch-off [4,10], respectively. To obtain (11) the ln term in (10), which prevails in weak inversion, has been considered constant for any drain current and equal to its value deep in weak inversion.

Eqns.(8) and (11) are alternative descriptions of MOSFET saturation owing to the effect of the carrier velocity saturation. (8) and (11) are valid from weak to strong inversion and clearly show the effect of bias (current level) on the saturation characteristics. The saturation voltage does not depend on the current for low current levels (i<sub>d</sub> <<1) and is proportional to the square root of the current for high current levels  $(i_d >> 1)$ . For very strong inversion (8) and (11) are no longer valid and (6) should be used to calculate the correct saturation charge.

# 4. MOSFET output conductance in saturation

In analog circuits MOSFETs frequently operate in the saturation region, where the transistor voltage gain can be made large. Explicit expressions of the output conductance in that region are useful for design purposes. We are going to show now how to use the results from the previous section in order to calculate the MOSFET output conductance.

From (5) one can write:

$$g_{d} = \frac{dI_{D}}{dV_{D}} = -Wv_{lim} \frac{dQ_{DSAT}^{'}}{dV_{D}}$$

(12)

The saturation charge  $Q_{IDSAT}$  depends on the channel length,  $L_{eq}$ , and on the inversion charge density at source,  $Q_{IS}$ . At this point we can include both the CLM and DIBL effects to calculate the small-signal output conductance. The channel length is generally written as  $L_{eq}$  =L-  $\Delta L$ , where  $\Delta L$  is the channel shrinkage. Many models have been tried to describe CLM [11]. Here we model the CLM as in [5]

$$\Delta L = \lambda \cdot L_{C} \ln \left[ 1 + \frac{V_{DS} - V_{DSSAT}}{L_{C} \cdot U_{CRTT}} \right]$$

(13)

where  $\lambda$  and  $L_{\text{C}}$  can be considered as fitting parameters. The DIBL effect is represented in our model by the DIBL parameter,  $\sigma$ , which models the dependence of the pinch-off voltage,  $V_{\text{P}}$ , on both the drain and source voltages according to:

$$V_{p}(V_{G}, V_{S}, V_{D}) = V_{p_{0}}(V_{G}) + \frac{\sigma}{n}(V_{D} + V_{S})$$

(14)

Now, (12), (13) and (14), together with (7) and (10), can be used to calculate the MOSFET output conductance to current ratio:

$$\frac{g_{d}}{I_{D}} = \frac{1}{V_{A}} = \frac{\lambda}{U_{CRIT}.L_{eq}} \cdot \frac{1}{1 + \frac{V_{DS} - V_{DSSAT}}{L_{C}.U_{CRIT}}} + \frac{\sigma}{n\phi_{t}} \frac{2}{\sqrt{1 + i_{d}} + 1}$$

(15)

Eqn.(15) is a generalization, for any bias conditions, of the MOSFET output conductance presented in [6]. One can readily notice that the CLM component of  $V_A$ , the Early voltage, depends only on the effective voltage drop across the shrunk part of the channel while the DIBL component depends on the current level  $i_d$ . The Early voltage is independent of the current level for weak inversion and increases in moderate inversion. For higher inversion levels the DIBL component of the Early voltage can be neglected compared to the CLM component.

From the above results it becomes clear that the new model (15) of the Early voltage proposed here includes the conventional Early voltage formulation as a limit case. (15) is valid as long as  $|Q'_{1S}| \ll Q'_{A}$ .

## 5. Results

MOSFETS from a 0.75 $\mu$ m technology with different channel lengths were measured for several bias conditions. Fig.1 displays the output characteristics of two MOSFETS with different channel lengths. The characteristics of the MOSFET with minimum channel length (L=0.75 $\mu$ m) are strongly affected by the DIBL effect in the weak inversion region.

Fig. 1. Output characteristics of NMOS transistor for  $V_G$  = 0.5, 0.6, 0.7, 0.9, 1.2, 1.6,2.0, 2.4, 2.8, 3.2, 3.6, 4.0, 4.4 V a) L = 0.75 $\mu$ m and b) L = 1.25 $\mu$ m

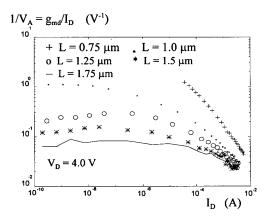

From Fig.2 we can conclude that the Early voltage increases with increasing lengths, is independent of the current level in weak inversion and increases in moderate and strong inversion as predicted by (15).

Fig.2. The output conductance to current ratio of NMOS transistors with channel length varying from 0.75μm to 1.25μm

Fig.3 shows that the Early voltage is almost independent of  $V_D$  in weak inversion. The comparison of Fig.3 a) and 3 b) shows that for the transistor with L=0.75 $\mu$ m the DIBL component of  $V_A$  is dominant and the CLM component becomes important as the channel length increases.

Fig.3. The output conductance to current ratio versus gate voltage with V<sub>D</sub> varying from 2.5V to 4.0V of NMOS transistors with a) L=0.75μm and b) 1.25μm

### 6. Conclusions

A compact charge-based model for the output conductance of the MOSFET has been presented. Some advantages of our model over BSIM3v3 are the use of simple expressions to describe all regions of operation as well as a smaller number of device parameters. The present model includes the conventional Early voltage formulation as a limit case and allows the calculation of the Early voltage in terms of physical parameters as well as bias conditions.

## Acknowledgments

The authors would like to thank CAPES and CNPq (from the Brazilian Ministries of Education and Science and Technology) for the financial support.

#### References

- Y. P. Tsividis, "Operation and Modeling of the MOS Transistor", New York: McGraw-Hill, 1987.

- [2] Y. Cheng and al, "A physical and scalable I-V model in BSIM3v3 for analog/digital simulation", IEEE Transactions on Electron Devices, vol. 44, n° 2, pp. 277-287, Feb. 1997.

- [3] Y. P. Tsividis, and K. Suyama, "MOSFET modeling for analog circuit CAD: problems and prospects", *IEEE Journal of Solid-State Circuits*, vol. 29, n° 3, pp. 210-216, Mar. 1994.

- [4] K. Lee, M. Shur, T. A. Fjeldly and T. Ytterdal, "Semiconductor device modeling for VLSI", Prentice Hall, Englewoods Cliffs, 1993.

- [5] C. C., Enz, F. Krummenacher and E. A. Vittoz, "An analytical MOS transistor model valid in all regions of operation and dedicated to low-voltage and low-current applications", Analog Integrated Circuits and Signal Processing Journal, vol. 8, pp. 83-114, Jul. 1995.

- [6] K. Toh, P. Ko, and R. G. Meyer, "An engineering model for short-channel MOS devices", *IEEE Journal of Solid-State Circuits*, vol. 23, n° 4, pp. 950-958, Aug. 1988.

- [7] M. A. Maher and C.A. Mead, "A physical chargecontrolled model for MOS transistors, in P. Losleben (ed.), Advanced research in VLSI", MIT Press, Cambridge, 1987.

- [8] B. Iniguez and E. G. Moreno, "A physically based C∞ continuous model for small-geometry MOSFET's", *IEEE Transactions on Electron Devices*, vol. 42, n° 2, pp. 283-287, Feb.1995.

- [9] A. I. A. Cunha, M. C. Schneider and C. Galup-Montoro, "An explicit physical model for the long-channel MOS transistor including small-signal parameters", *Solid-State Electronics*, vol. 38, n° 11, pp. 1945-1952, Nov. 1995.

- [10] A. I. A. Cunha, O. C. Gouveia Filho, M. C. Schneider and C. Galup-Montoro, "A current-based model of the MOS transistor", *Proc. 1997 Int. Symposium on Circuits* and Systems, pp. 1608-1611, Hong-Kong, Jun. 1997.

- [11] A. Chatterjee, C. F. Machala, III and P. Yang, "A submicron DC MOSFET model for simulation of analog circuits", IEEE Trans. on Computer-Aided Design of Integrated Circuits and Systems, vol.14, no. 10, pp. 1193-1207, Oct. 1995.