## CAPÍTULO 4 CIRCUITOS LÓGICOS COMBINACIONAIS CMOS

Oscar C. Gouveia Filho

Departamento de Engenharia Elétrica

UFPR

URL: www.eletrica.ufpr.br/ogouveia E-mail: ogouveia@eletrica.ufpr.br

### **OBJETIVOS**

- 1. Analisar e projetar portas lógicas CMOS

- 2. Analisar e projetar portas complexas CMOS

- 3. Fazer o layout de células CMOS

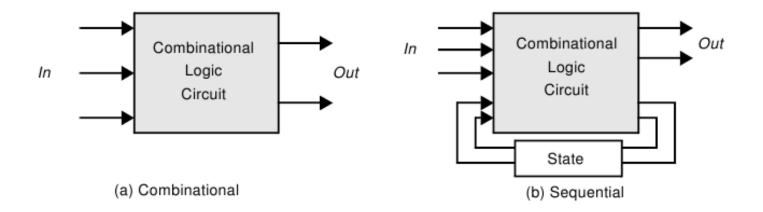

## CIRCUITOS LÓGICOS COMBINACIONAIS E SEQUENCIAIS

### PORTAS ESTÁTICAS CMOS

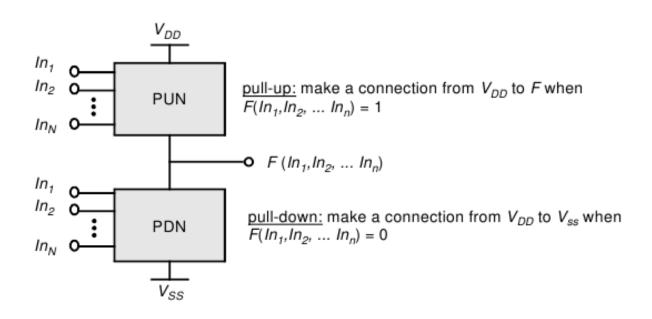

## Portas estáticas CMOS são formadas por duas redes complementares

## Observações para construção das redes PUN e PDN

- Os transistores devem ser vistos como chaves controladas pela tensão aplicada à sua porta.

- PDN é composta por transistores NMOS.

- PUN é composta por transistores PMOS.

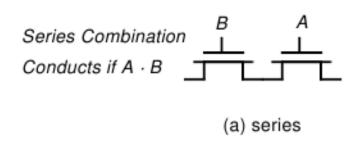

- Transistores NMOS conectados em série realizam uma função AND.

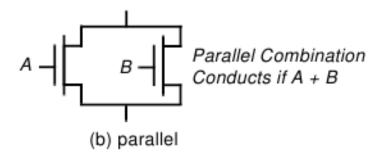

- Transistores NMOS conectados em paralelo realizam uma função OR.

Transistores PMOS conectados em série realizam uma função NOR.

• Transistores PMOS conectados em paralelo realizam uma função NAND.

- Usando os teoremas de De Morgan pode-se mostrar que as redes PUN e PDN são duais, ou seja, uma conexão paralela de transistores na rede PUN corresponde a uma conexão série na rede PDN.

- As portas complementares são naturalmente inversoras.

Portanto, só é possível implementar as funções NAND, NOR, XNOR. Para implementar as portas AND, OR, XOR é necessário mais um estágio.

- •O número de transistores necessários para implementar uma porta de N entradas é 2N.

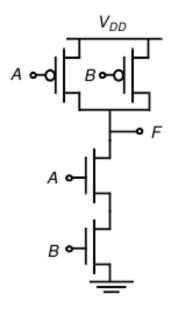

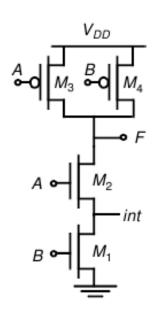

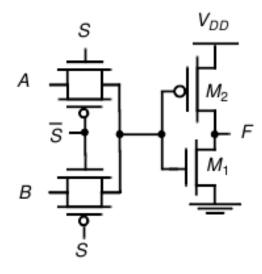

## **EXEMPLO: PORTA NAND**

Table 6.1Truth Table for 2 input NAND

| Α | В | F |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

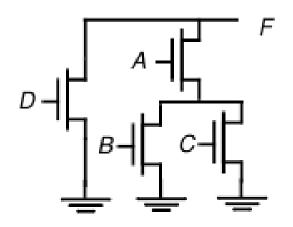

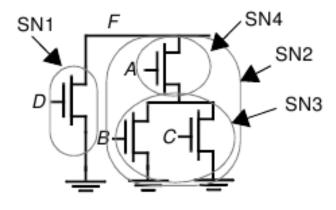

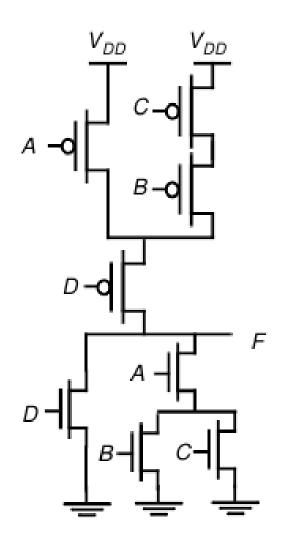

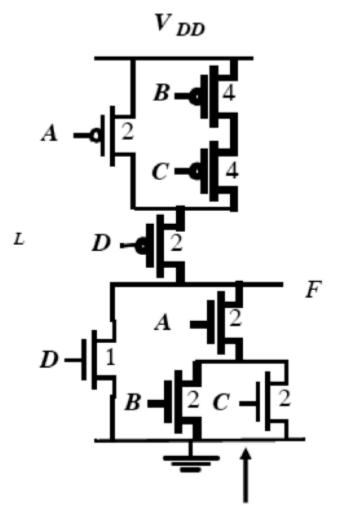

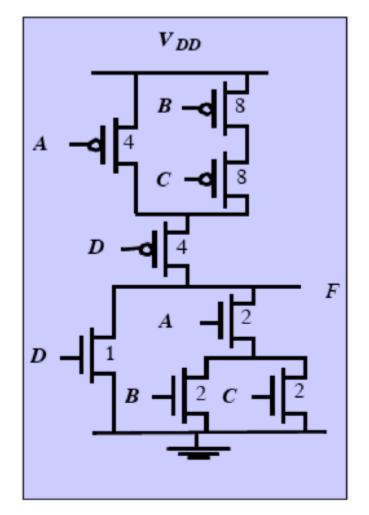

## **EXEMPLO: PORTA LÓGICA COMPLEXA**

$$F = \overline{D + A.(B + C)}$$

### **PDN**

## **PUN**

### Dimensionamento dos transistores

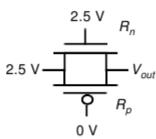

Here it is assumed that  $R_p = R_n$

#### Exercícios:

a)

$$Y = \overline{ABC + D}$$

b)

$$Y = (\overline{AB + C}) \cdot \overline{D}$$

c)

$$Y = \overline{AB + C \cdot (A + B)}$$

# CARACTERÍSTICAS ESTÁTICAS DE PORTAS CMOS COMPLEMENTARES

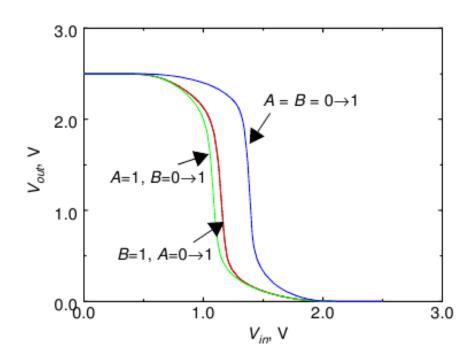

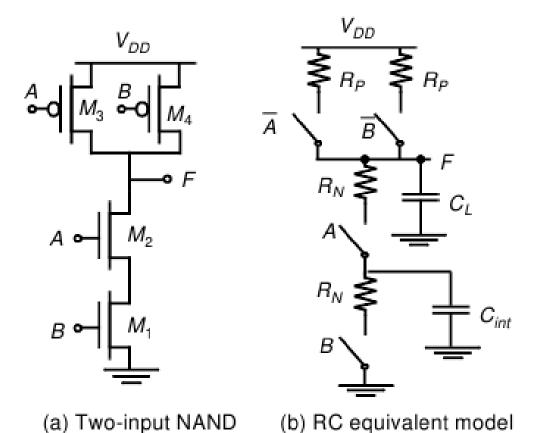

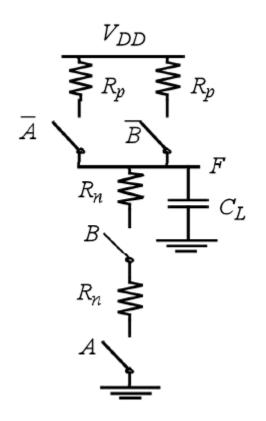

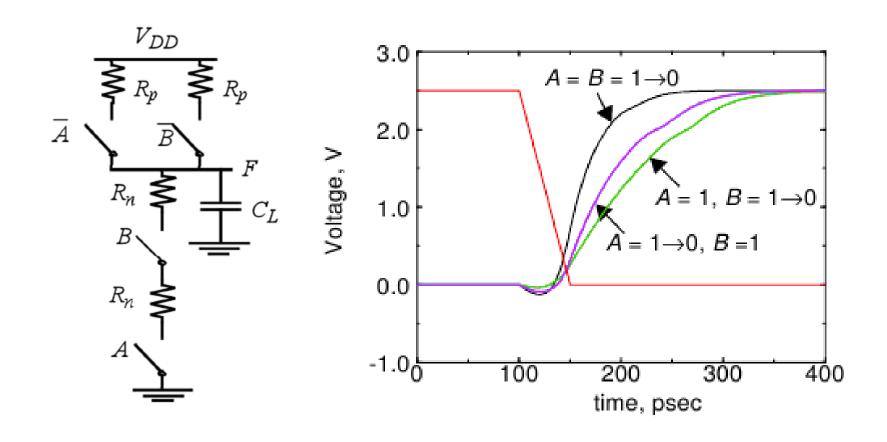

## ATRASO DE PROPAGAÇÃO EM PORTAS CMOS COMPLEMENTARES

## ATRASO DE PROPAGAÇÃO EM PORTAS CMOS COMPLEMENTARES

$$t_p = 0.69 \, R \, C$$

#### Input Data Pattern

$$A = B = 0 \rightarrow 1$$

$$A = 1, B = 0 \rightarrow 1$$

$$A = 0 \rightarrow 1, B = 1$$

$$A=1, B=1\to 0$$

$$A = 1 \rightarrow 0, B = 1$$

$$t_{pHL}=0.69(2R_n)C_L$$

$$t_{pHL} = 0.69 (2R_n) C_L$$

$$t_{pLH} = 0.69 (R_p/2) C_L$$

$$t_{pLH} = 0.69 R_p C_L$$

## ATRASO DE PROPAGAÇÃO EM PORTAS CMOS COMPLEMENTARES

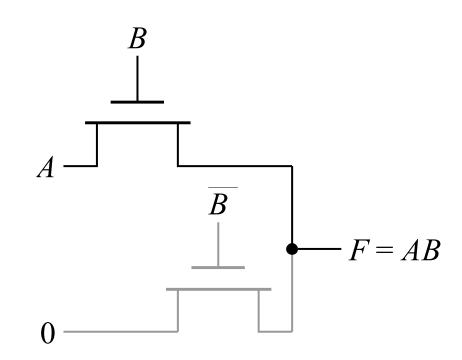

## LÓGICA COM PORTAS DE TRANSMISSÃO

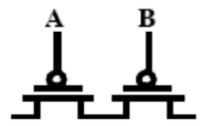

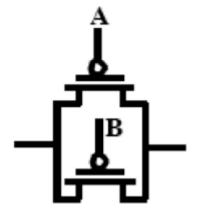

### Transistor de passagem

**Porta AND**

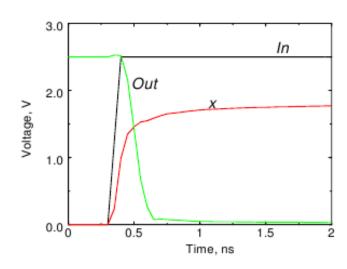

### Excursão de tensão no transistor de passagem

#### **Problemas:**

- transistor NMOS passa um "1" pobre

- à medida que a tensão de saída se aproxima de seu valor final a velocidade da transição diminui

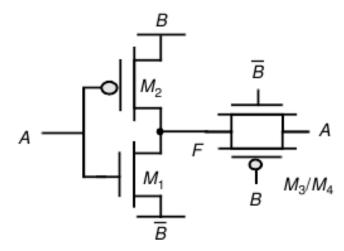

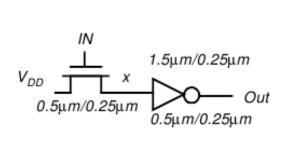

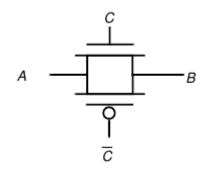

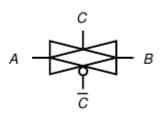

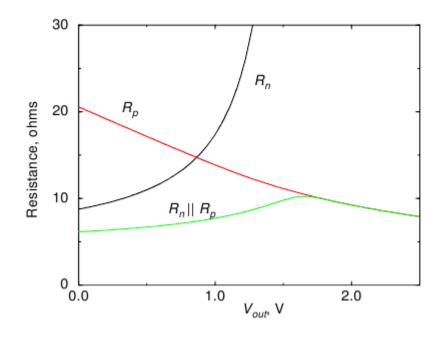

### **PORTA DE TRANSMISSÃO**

### Solução para ambos os problemas

### **Exemplo: Multiplexador**

$$\overline{F} \ = \ (A \cdot S + B \cdot \overline{S})$$

### **Exemplo: porta XOR**